## ARCHITETTURE M-CNN

V. Bonaiuto, F. Sargeni

Dipartimento di Ingegneria Elettronica Università di Roma Tor Vergata Via del Politecnico 1, 00133 ROMA

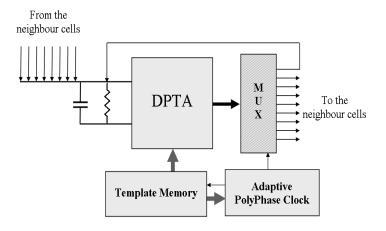

Il Laboratorio di Teoria dei Circuiti dell'Università di Roma "Tor Vergata" ha sviluppato, sin dal 1993, una famiglia di neurochip (DPCNN – Digitally Programmable Cellular Neural Networks) che presenta come principale caratteristica quella di essere un'architettura dedicata all interconnettibilità di vari chip al fine di ottenere la realizzazione di reti di dimensioni sempre più ampie [1]. Tali neurochip sono dei circuiti basati sul modello di CNN (Cellular Neural Networks) proposto dal Prof. L.O. Chua nel 1988. Essi sono circuiti dedicati analogici di tipo current-mode i cui pesi sinaptici sono programmabili in modo digitale. Il cuore di ciascuno di questi neurochip è rappresentato da un particolare circuito il DPTA (Digitally Programmable Transconductance Amplifier) [2] per mezzo del quale, è possibile la selezione digitale del parametro di transconduttanza e, di conseguenza, dei pesi sinaptici della rete. In particolare, nei due chip realizzati (3x3DPCNN e 6x6DPCNN), ciascuna delle singole celle CNN è stata progettata utilizzando un diverso DPTA per ciascuno dei pesi della matrice di interconnessione. In particolare nove DPTA sono stati utilizzati per implementare i termini della matrice A (vicinato 1) più un ulteriore DPTA per implementare sia il termine di Bias che il Template B.

L'idea alla base di questa attività di ricerca consiste nel progetto di una nuova cella CNN (M-CNN – Multiplexed CNN) nella quale uno stesso circuito DPTA sia in grado di generare, utilizzando un approccio a divisione di tempo, ciascuno dei contributi in corrente necessari a tutte le celle del vicinato. In particolare, sono stati studiati nuovi circuiti con caratteristiche tali da soddisfare le specifiche dell'approccio a divisione di tempo in termini di capacità di programmazione del termine transconduttanza come pure nella velocità del tempo di risposta [4-5].

Il sistema proposto è in grado di ridurre significativamente il numero dei moltiplicatori analogici all'interno di ciascuna cella permettendo una rilevante diminuzione (circa 80%) dell'area di silicio occupata dalla parte analogica rispetto alla precedente architettura. Una analoga metodologia è già stata usata dagli stessi autori in precedenti progetti al fine di ridurre il numero dei pad necessari alle interconnessioni in sistemi CNN multi-chip [3]. In entrambi i casi, la metodologia proposta introduce del rumore di tipo additivo al segnale analogico in uscita senza alterare, tuttavia, la funzionalità delle stesse operazioni CNN.

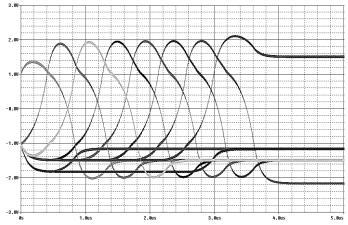

L'approccio è stato applicato con successo su reti con connessione di tipo classico cosi come su una rete con connessione a stella [6-9]. In Fig. 1 è mostrato lo schema a blocchi di una singola cella della rete mentre Fig. 2 mostra la simulazione elettrica di una rete M-CNN formata da una riga di dieci celle che esegue una operazione di CCD.

## **Bibliografia**

- [1] M. Salerno, F. Sargeni, V. Bonaiuto: "A Dedicated Multi-Chip Programmable System for Cellular Neural Networks", Analog Integrated Circuits and Signal Processing, Kluwer Academic Publisher, Vol.18, no. 2/3, February 1999, pages.277-288.

- [2] F. Sargeni: "Digitally Programmable Transconductance Amplifier for CNN Application", Electronics Letters, vol.30, no.11, pages. 870-872, May 1994.

- [3] M. Salerno, F. Sargeni, V. Bonaiuto: "An improved Architecture for the interconnections in a multi-chip CNN system", Proc. IEEE Int. Conf. on Circuits and Systems (ISCAS 1998), 1998, vol.3, pages. 143-146.

- [4] F. Sargeni; V. Bonaiuto; M. Bonifazi, "TD-DPTA Cellular Neural Network Cell", 8th IEEE Intern. Workshop on Cellular Neural Networks and Their Applications, CNNA 2004, 22-24 Jul 2004.

- [5] F. Sargeni; V. Bonaiuto; M. Bonifazi, "Time division digital programmable OTA for cellular neural networks", Proceedings of the ECCTD 2005, Page(s): 75 78, vol. 1, 2005.

- [6] F. Sargeni; V. Bonaiuto; M. Bonifazi, "Multiplexed Circuit for Star-CNN Architecture", Proceedings of the CNNA 2006, Page(s):1 5, 2006

- [7] F. Sargeni; V.Bonaiuto: "Programmable Non-Linearity for Neural Networks Applications", 52nd IEEE Midwest Symposium on Circuits and Systems (MWSCAS 2009), Cancun, Mexico Page(s): 881-884

- [8] F. Sargeni, V. Bonaiuto: "Programmable Non-Linearity for Star Cellular Neural Networks", European Conference on Circuits Theory and Design (ECCTD 2009), Antalya, Turkey, Page(s): 547-550.

- [9] F. Sargeni; V.Bonaiuto: "VLSI circuits for multiplexed Star CNNs", Proceedings of the CNNA 2010 Page(s): 1-4

Fig. 1 Schema a blocchi di una cella M-CNN

Fig. 2 Simulazione di una operazione di CCD con rete M-CNN.